# **Outline of Lecture**

- The ALU Control Operation & Design

- The Datapath Control Operation & Design

# **ALU Control**

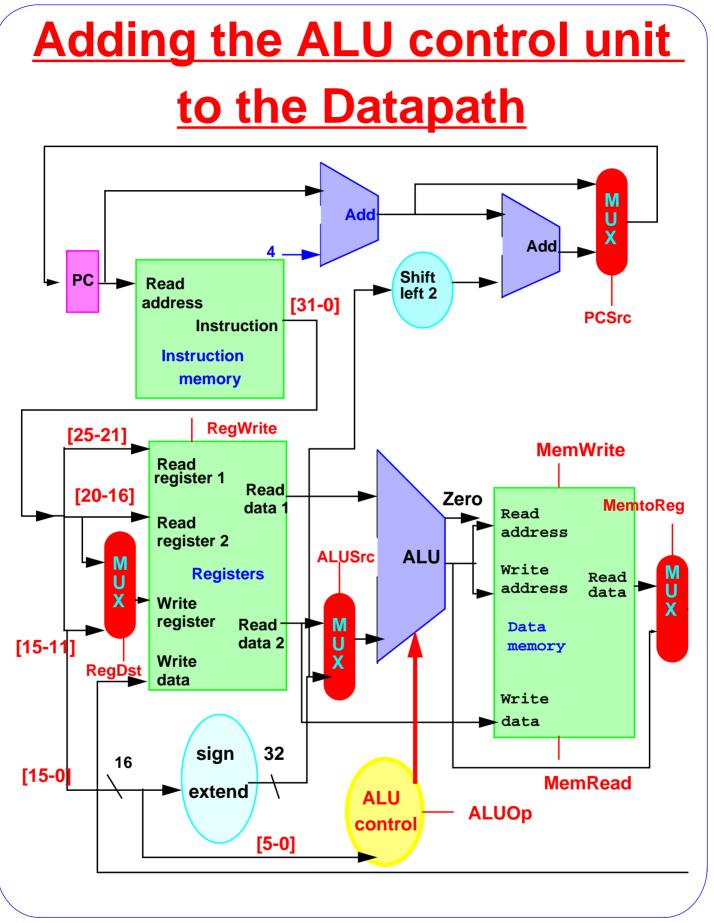

- After the design of partial single MIPS datapath, we need to add the *control unit* that controls the whole operation of the datapath (generatse appropriate signals for the operation of the datapath).

- From the previous chapter when we designed the ALU these are the ALU control signals that we came up with:

| ALU Control lines | Function |

|-------------------|----------|

| 0 00              | AND      |

| 0 01              | OR       |

| 0 10              | ADD      |

| 1 10              | SUB      |

| 1 11              | SLT      |

- For load and store, we need to calculate the memory address by addition.

- For R-type instructions, the ALU needs to perform one of five operations (Subtract, add, AND, OR, SLT) depending on the value of the 6-bit funct filed.

# **ALU Control**

- For branch equal, the ALU must perform a subtraction.

- By using the *function field* (6 bits for MIPS), the table above can be expanded to cover a wider range of instructions.

| Instruction<br>opcode | ALUOp | Instruction operation | Function<br>code | Desired<br>ALU<br>action | ALU<br>control<br>input |

|-----------------------|-------|-----------------------|------------------|--------------------------|-------------------------|

| LW                    | 00    | load word             | XXXXXX           | add                      | 010                     |

| SW                    | 00    | store word            | XXXXXX           | add                      | 010                     |

| Branch<br>equal       | 01    | branch<br>equal       | XXXXXX           | subtract                 | 110                     |

| R-type                | 10    | add                   | 100000           | add                      | 010                     |

| R-type                | 10    | subtract              | 100010           | subtract                 | 110                     |

| R-type                | 10    | AND                   | 100100           | and                      | 000                     |

| R-type                | 10    | OR                    | 100101           | or                       | 001                     |

| R-type                | 10    | SLT                   | 101010           | slt                      | 111                     |

- In order to design the logic for this ALU control unit, we create a truth table.

- The input of the truth table is a 2-bit ALUOp and a 6-bit Function code, and the output is a 3-bit ALU control signals

| ALUOp  |        | Function code |    |           |    |           |    | Operation |

|--------|--------|---------------|----|-----------|----|-----------|----|-----------|

| ALUOp1 | ALUOp2 | F5            | F4 | <b>F3</b> | F2 | <b>F1</b> | F0 |           |

| 0      | 0      | Х             | X  | X         | X  | X         | X  | 010       |

| X      | 1      | Х             | X  | X         | X  | X         | X  | 110       |

| 1      | X      | Х             | X  | 0         | 0  | 0         | 0  | 010       |

| 1      | X      | Х             | X  | 0         | 0  | 1         | 0  | 110       |

| 1      | X      | Х             | X  | 0         | 1  | 0         | 1  | 001       |

| 1      | X      | Х             | X  | 1         | 0  | 1         | 0  | 111       |

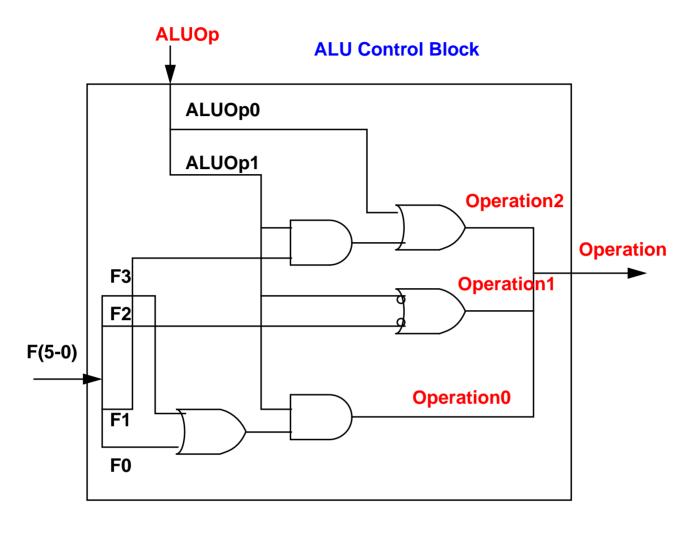

• Using the above truth table, we can design the ALU control unit:

#### Lecture 25

6

**HKUST**

**Computer Science**

#### The function of each of the control signals in the datapath is given in the following table:

| Signal name | Effect when deasserted                                                                 | Effect when asserted                                                                                     |

|-------------|----------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------|

| MemRead     | None                                                                                   | Data memory contents at<br>the read address are put<br>on read data output                               |

| MemWrite    | None                                                                                   | Data memory contents at<br>address given by write<br>address is replaced by<br>value on write data input |

| ALUSrc      | The second ALU operand comes from the second reg-<br>ister file output                 | The second ALU operand<br>is the sign-extended lower<br>16-bits of the instruction                       |

| RegDst      | The register destination<br>number for the write regis-<br>ter comes from the rt field | The register destination<br>number for the write regis-<br>ter comes from the rd field                   |

| RegWrite    | None                                                                                   | The register on the write<br>register input is written<br>into with the value on the<br>write data input |

| PCSrc       | The PC is replaced by the output of the adder that computes the value of PC+4          | The PC is replaced by the<br>output of the adder that<br>computes the branch tar-<br>get                 |

| MemtoReg    | The Value fed to the register<br>write data input comes from<br>the ALU                | The value fed to the regis-<br>ter write data input comes<br>from the data memory                        |

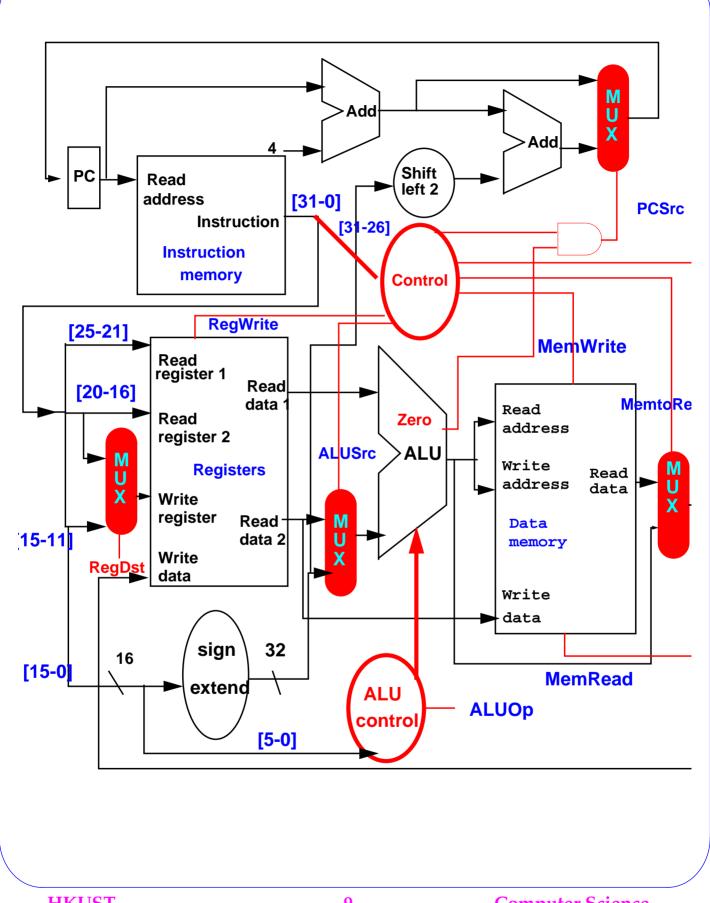

The control signals can be set by the datapath control unit based only on the *opcode field of the instruction*.

The only exception is the <u>*PCSrc*</u> control line. It should be set if the instruction is a branch on equal and the Zero output of the ALU is true.

To generate the PRSrc signal, we will AND toegther a signal from the control unit, called **branch**, with the Zero signal out of the ALU.

The Whole Datapath including all the control signals will be as follows:

#### Lecture 25

**HKUST**

**Computer Science**

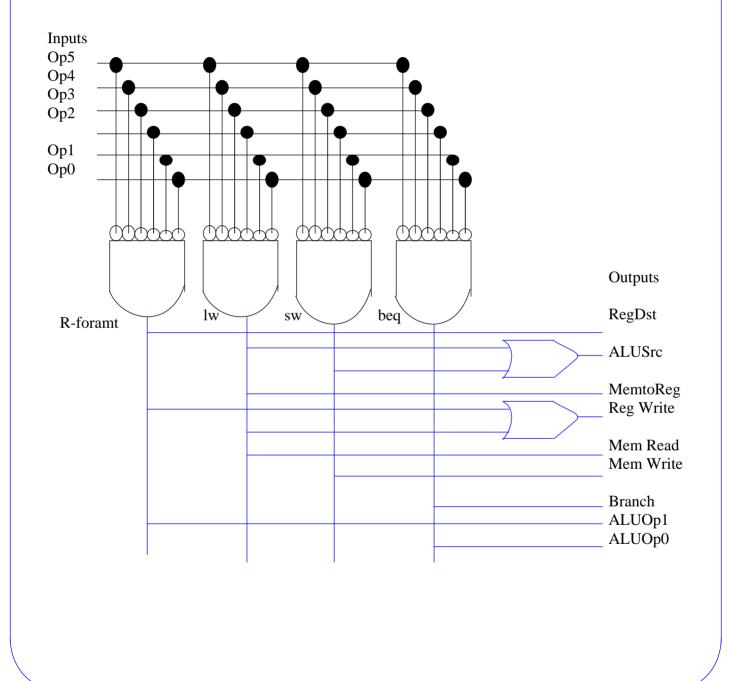

# The logic circuits for the datapath control unit.

The setting of the control lines is completely determined by the opcode fields of the instruction.

| Instructio<br>n | Reg<br>Dst | ALU<br>Src | Memto<br>Reg | Reg<br>Write | Mem<br>Read | Mem<br>Write | Branch | ALU<br>Op1 | ALU<br>Op2 |

|-----------------|------------|------------|--------------|--------------|-------------|--------------|--------|------------|------------|

| R-format        | 1          | 0          | 0            | 1            | 0           | 0            | 0      | 1          | 0          |

| lw              | 0          | 1          | 1            | 1            | 1           | 0            | 0      | 0          | 0          |

| sw              | Х          | 1          | X            | 0            | 0           | 1            | 0      | 0          | 0          |

| beq             | X          | 0          | X            | 0            | 0           | 0            | 1      | 0          | 1          |

#### The input to the datapath control unit:

|          | Oneede in            | Opcode in binary |     |     |     |     |     |  |

|----------|----------------------|------------------|-----|-----|-----|-----|-----|--|

| Name     | Opcode in<br>decimal | Op5              | Op4 | Op3 | Op2 | Op1 | Op0 |  |

| R-format | 0                    | 0                | 0   | 0   | 0   | 0   | 0   |  |

| lw       | 35                   | 1                | 0   | 0   | 0   | 1   | 1   |  |

| sw       | 43                   | 1                | 0   | 1   | 0   | 1   | 1   |  |

| beq      | 4                    | 0                | 0   | 0   | 1   | 0   | 0   |  |

#### Lecture 25

#### **comp 180**

# Truth Table of the Datapath Control Unit

|         |          | R-format | lw | SW | beq |

|---------|----------|----------|----|----|-----|

|         | Op5      | 0        | 1  | 1  | 0   |

|         | Op4      | 0        | 0  | 0  | 0   |

| Inputs  | Ор3      | 0        | 0  | 1  | 0   |

|         | Op2      | 0        | 0  | 0  | 1   |

|         | Op1      | 0        | 1  | 1  | 0   |

|         | Op0      | 0        | 1  | 1  | 0   |

|         | RegDst   | 1        | 0  | X  | Х   |

|         | ALUSrc   | 0        | 1  | 1  | 0   |

|         | MemtoReg | 0        | 1  | X  | Х   |

| Outputs | RegWrite | 1        | 1  | 0  | 0   |

|         | MemRead  | 0        | 1  | 0  | 0   |

|         | MemWrite | 0        | 0  | 1  | 0   |

|         | Branch   | 0        | 0  | 0  | 1   |

|         | ALUOp1   | 1        | 0  | 0  | 0   |

|         | ALUOp2   | 0        | 0  | 0  | 1   |

Lecture 25

## **Implementation**

• We can easily implement the above truth table using simple gates. If we used all possible instructions, then a PLA would be more appropriate.

## **Further Reading**

<u>Chapter 5 & Appendix B.</u> David A. Patterson and John L. Hennessy. *Computer Organization & Design: The Hardware / Software Interface*. Morgan Kaufman Publishers, 1998 (page 350-370).